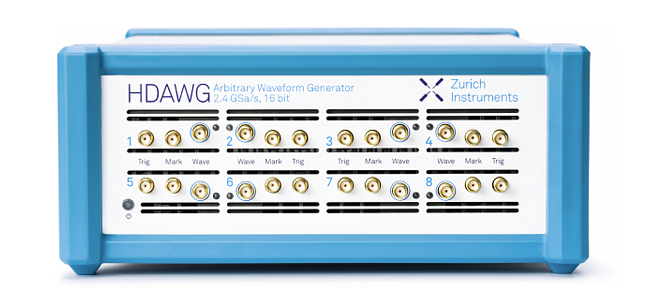

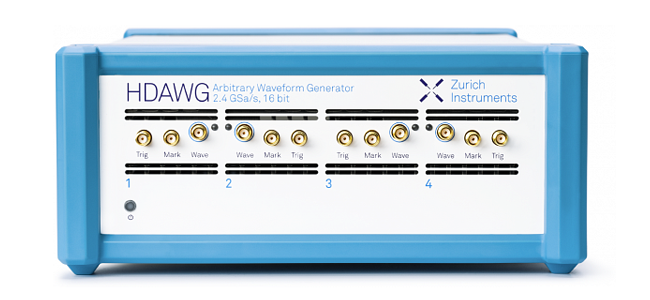

Zurich Instruments HDAWG マルチチャネル任意波形発生器 (AWG) は、このクラスでは最高のチャネル密度の利用が可能で、最高750 Mhz帯域までの高度信号生成に対応しています。HDAWGには、4または8個のDCカップリング、シングルエンド アナログ出力チャネルが搭載され、16ビットの垂直解像度を実現します。出力は、最大帯域と高度ノイズパフォーマンスが可能なダイレクトモードと、信号振幅を最大5 Vpp まで引き上げる増幅モードとの間で個別切替が可能です。チャネルごとに2つのマーカがあるため、16ビットのフル出力解像度が維持しながらも、高精度セットアップ同期化を実現します。

LabOne® は、最新プログラミングコンセプトを採用し、使いやすい関数発生器を備えたAWGのパフォーマンスと柔軟性を実現します。プラットフォームが独立した LabOne ユーザーインターフェース (UI) とLabVIEW®、.NET, MATLAB®、C、および Python向けAPIは、既存の制御環境の簡単な測定オートメーションと高速統合を可能にします。

特長

- 2.4 GSa/s、16 ビット、750 MHz 信号帯域

- 5 Vpp 最大振幅

- 64 出力チャネルまで拡張可能

- 最高チャネル密度が利用可能

- 出力遅延のトリガは 50 ns 以下

- 複数の周波数でデジタル変調

- LabOne® AWG シーケンサとコンパイラ

ハイライト

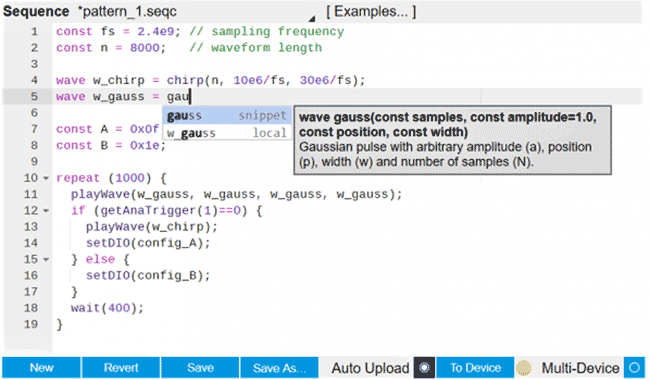

高レベル AWG プログラミング

LabOne UI は、直截、簡単に読みやすいようにハードウェア制御することで、すぐに使用できるように設計されています。LabOne AWG シーケンサで波形とシーケンスを定義した後、LabOne AWG コンパイラが指示を機械語に変換し、その結果をハードウェアに最短時間で転送します。LabOne シーケンシングは、動的に変化する遅延および条件付きブランチングポイントで、ループをサポートします。

標準波形、例えば、ガウス、ブラックマン、sinc など以外に、 LabOne には、複雑な波形設計に必要な数理および配列編集ツールがすべて含まれています。波形は簡単に追加、乗算、カットおよび連結するか、またはセグメントで構成することができます。測定した信号または MATLAB など、別のツールで計算した波形のインポートは、ドラッグ・アンド・ドロップの簡単操作で可能です。

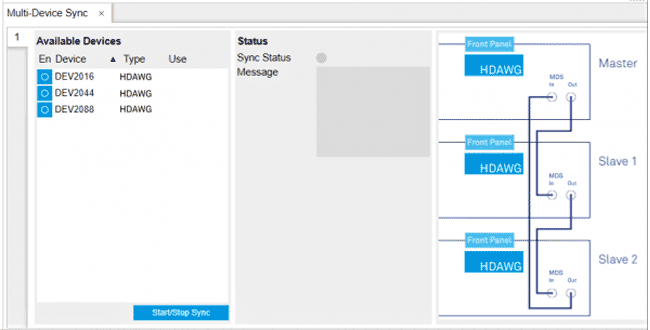

複数機器同期化 (MDS)

MDS により、複数の HDAWG を1基の多チャネル AWG で十分、操作することができます。

- 1基の UI/API ですべての機器を操作

- 全出力チャネルの絶対同期化

- 全機器クロックの位相ロック

- UHF シリーズ機器の時刻スタンプとサンプリングレートの同期化

複数機器の使用時、LabOne AWG コンパイラは、マスターシーケンスプログラムを全機器に分配する作業を行います。自動トリガ交換プロトコルは同期化再生タイミングを実現します。MDS を使用することで、 ロックイン増幅器、ボックスカー、デジタイザ および AWG 機能を含む、全信号生成および吸収システムを最大 600 MHz まで積載することもできます。

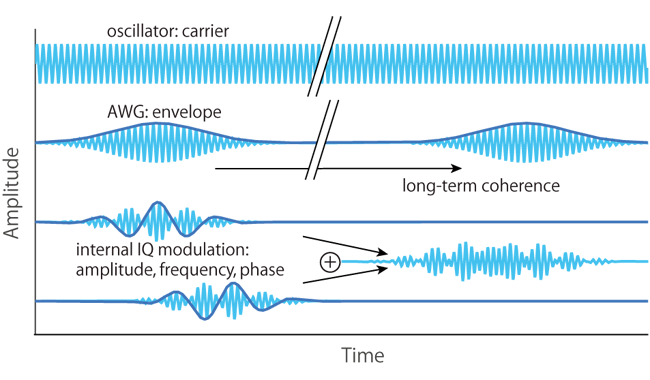

発振器、変調および位相制御

HDAWG には、プログラムされた AWG エンベロープ信号とは独立して、信号の正弦搬送波を生成するデジタル発振器が装備されています。これは、多数のパルス間で、長い信号を非常に高速波形アップロードと高精度位相コヒーレンスで発振できることを意味しています。静的波形に書き込まれる場合がある搬送波周波数と位相は、自由に調節および掃引できます。

HDAWG-MF 多周波数オプション は、デジタル I/Q 変調、周波数マルチプレックシング、または位相サイクリングにより、発振数を増やし、フルデジタル I/Q 変調周波数および位相変調を可能にします。

HDAWG-FG 関数発生器 オプションでは、変調コンセプトが正弦搬送波の範囲を超え、搬送波の波形を生成します。

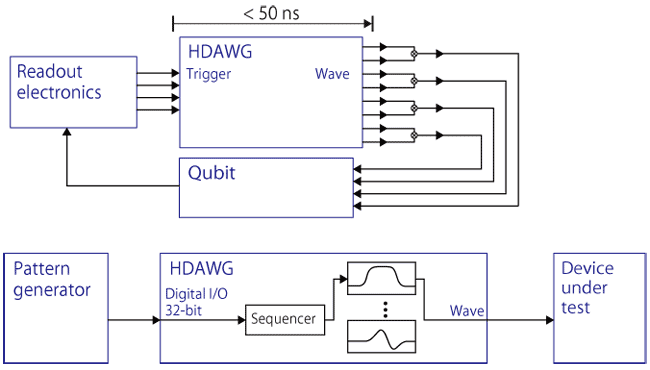

低遅延トリガとシーケンスブランチング

低遅延設計により、HDAWG は、正面パネルのトリガ入力の1つで外部トリガを検出後、50 ns 以下の信号出力で最初のサンプルを生成することができます。これは、機器特性が短寿命で、ナノ秒削減ごとにじっけぬえの結果が顕著に改善される量子コンピューティングのフィードバック実験 には必須です。本機器の4または8出力チャネルを2または4単位にグループ分けすることができます。その結果、これらグループのそれぞれを個別にトリガできるため、機器またはセットアップの個別部位に信号を送信する場合の柔軟性が向上します。

高複雑さとリアルタイム制御により信号を生成するため、HDAWG は、32 ビットデジタル入力に適用されるビットパターンをベースにしたプログラマブルメモリに、最大 1024 の事前保存波形から選択することができます。これはデジタル変調パターン、機器別検査波形、または マルチキュービット 状態の読出結果を表す場合があります。

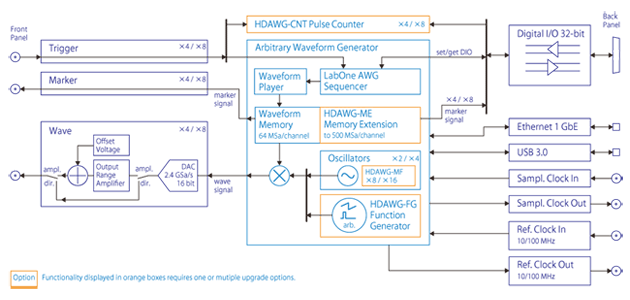

機能系統図

仕様

任意波形発生器

| チャネル | 4 (HDAWG4) または 8 (HDAWG8) |

|---|---|

| 垂直解像度 | 16 ビット |

| チャネルごとの波形 | 64 MSa; |

| メモリ | 500 MSa (HHDAWG-ME オプション付き) |

| シーケンスメモリ | 16384 使用方法 |

| 波形粒度 | 8 サンプル |

| 最小波形長 | 32 サンプル |

| シーケンスクロック 周波数 |

8で除したサンプリングレート |

| シーケンサの使用方法 (再生) |

再生波形 (単または多チャネル)、 再生波形セグメント (開始サンプル指数とセグメント長)、 ライブラリの再生波形 (DIO 入力状態)、割込み波形再生 |

| シーケンサ使用方法 (その他) |

定数待機、トリガ待機、トリガ状態の設定/取得、 DIO 状態の設定/取得、整数可変演算 (加減、論理演算)、 発振器周波数/位相の変更 (リアルタイム)、 他の機器設定の変更 (非リアルタイム) |

| シーケンサ制御構造 | 繰り返し (1 ~ 223-1 または無限)、 条件付きブランチ (マルチブランチ) |

波形出力

| コネクタタイプ | SMA |

|---|---|

| 出力インピーダンス | 50 Ω |

| 出力カップリング | DC |

| 出力モード | 増幅、ダイレクト |

| 出力範囲 (最大 50 Ω) | 0.2 ~ 5.0 Vpp (増幅) 0.8 Vpp (ダイレクト) |

| 補正電圧 (最大 50 Ω) | 0.5 × ピーク電圧、最大±1.25 V (増幅) 0 V (ダイレクト) |

| 位相ノイズ | <−110 dBc/Hz (100 MHz、補正 10 kHz) |

| 電圧ノイズ | 30 nV/√Hz (増幅、5 Vpp レンジ) |

| 200 kHz 以上 | 12 nV/√Hz (ダイレクト) |

時刻と周波数領域特性

| frequency range, max. | 0 − 300 MHz, 5.0 Vpp |

|---|---|

| amplitude into 50 Ω | 0 − 750 MHz, 0.8 Vpp |

| サンプリングクロックソース | 内部、外部 |

| サンプリングレート | 1.5 kSa/s ~ 2.4 GSa/s (内蔵クロック) 50 Msa/s/s ~ 2.4 GSa/s (外部クロック) |

| 内蔵サンプリング クロック分解能 |

7桁 |

| 上昇時間 (20% ~ 80%) | < 550 ps (増幅、1 V ごと、5 Vpp 出力レンジ) < 300 ps (ダイレクト、0.8 V ごと) |

| 出力に対するトリガ遅延 | < 50 ns |

| チャネル間のスキュー | < 200 ps (任意の2チャネル) |

| < 20 ps (チャネル 1と2、3と4、...) | |

| スキュー調節範囲 | 10 ns |

| スキュー調節分解能 | 10 ps |

Marker & Other Outputs

| マーカー出力 | チャネルごとに2、正面パネルのチャネルごとに1 SMA 出力、 裏面パネルの DIO の追加出力 |

|---|---|

| サンプリングクロック出力 | 裏面パネルの SMA |

| サンプリングクロック出力振幅 | 2 Vpp |

| 基準クロック出力 | 裏面パネルの SMA |

| 基準クロック出力振幅 | 1 Vpp |

| 基準クロック出力周波数 | 10 / 100 MHz |

入力

| トリガ入力 | チャネルごとに1、正面パネルのSMA |

|---|---|

| トリガ入力インピーダンス | 50 Ω / 1 kΩ |

| トリガ入力振幅範囲 | ±5 V (50 Ω) ±10 V (1 kΩ) |

| トリガ入力閾値範囲 | ±5 V (50 Ω) ±10 V (1 kΩ) |

| トリガ入力閾値分解能 | < 0.4 mV |

| サンプリングクロック入力 | 裏面パネルの SMA |

| 基準クロック入力 | 裏面パネルの SMA |

| 基準クロック入力周波数 | 10 / 100 MHz |

最大定格

| 損傷閾値サンプリング クロック入力 |

±5 V |

|---|---|

| 損傷閾値基準入力 | ±5 V |

接続およびその他

| デジタル IO (DIO) | VHDCI 68 ピン メスコネクタ、32 ビット、 入力または出力設定可、3.3 V TTL |

|---|---|

| ホスト接続 | LAN / イーサネット、1 Gbit/s USB 3.0、5 Gbit/s |

| PC メモリ要件 | 4 GB+ |

| PC CPU 要件 | 所定の SSE2 説明書記載セットとの互換性 例: AMD K8 (Athlon 64, Sempron 64, Turion 64 など)、 AMD Phenom、Intel Pentium 4、Xeon、Celeron Celeron D、Pentium M, Celeron M、Core、Core 2 Core i5、Core i7、Core i3、Atom |

| オペレーティングシステム | LabOne との互換性 参照 |

全般

| 寸法 | 43.0 × 23.2 × 10.2 cm 16.9 × 9.2 × 4.0 インチ、19 インチ ラックに適合 |

|---|---|

| 重量 | 4.6 kg、10.2 lbs |

| 電源供給 AC ライン | 100~240 V (±10%)、50/60 Hz |

| 作動温度 | +5 °C ~ +40 °C |

| 動作環境 | IEC61010、室内の場所、設置カテゴリ II、汚染度 2 |

| 動作高度 | 最高 2,000 メートル |

-

※製品仕様は改良などにより、予告なしに変更となる場合あります。

応用

- 量子コンピューティング

- RADAR / LIDAR

- NMR および EPR 分光器

- 半導体素子の検査

- MRI および通信で MIMO 技術利用

HDAWG は、基本 AWG 機能を 追加波形メモリ、関数発生器機能、内蔵発振器およびパルスカウンタ セットにより拡張し、厳しい用途条件の要望に対応するハイエンド機器です。

量子コンピューティングと位相配列レーダー

複数の HDAWG 機器をシングルユーザーインターフェースを使用して制御および自動同期化できるため、これまで必要だった複雑さや実験スペースを削減しながら、レーダと量子コンピューティングシステムの効率計量を可能にします。外部トリガ信号に対する応答時間が 50 ns と短いことで、高精度な量子誤差修正方法が実現します。内蔵発振器は波形アップロード時間を最短にして、位相コヒーレンスを実現、波形定義がより簡単になります。統合型パルスカウンタでは、捕捉イオンおよび N-V センター実験向けのセットアップを簡素化。

NMR と分光器

NMR およびその他分光器使用での信号は、ナノ秒から最大で数秒の間隔で発生します。HDAWG は、可変サンプリングレートおよび/またはパラメーター掃引を適用して、これらの測定をスピードアップすることができます。デジタル変調を使用して、作業負荷を追加しないで位相コヒーレンスを維持しながら、最小の波形アップロード時間で1つ以上の搬送波信号に任意エンベロープをかけることができます。

半導体素子の検査

入れ子シーケンシング、波形反復、および DIO 制御対応のダイナミックシーケンシングは、幅広い高スループット検査用信号の実現に最適です。AWG 関数発生器信号を乗算または追加すると、可能性が拡張され、日常の測定ルーチンの簡素化および高速化に役立ちます。

製品一覧

任意波形発生器 HDAWG8

任意波形発生器 HDAWGの8チャネル変形型です。

周波数帯、垂直分解能、およびその他の信号生成仕様については、この機器は HDAWG4 4チャネル変形型と同じです。

任意波形発生器 HDAWG4

任意波形発生器 HDAWGの4チャネル変形型です。

周波数帯、垂直分解能、およびその他の信号生成仕様については、この機器は HDAWG8 8チャネル変形型と同じです。

-

※4チャネル変形型は、8チャネル変形型へのアップグレードはできません。

オプション

HDAWG-CNT パルスカウンタは、最大8個のパルス列分析を並行して実施でき、イベントベースの測定、例えば、光電子倍増管を使用した光子検出で最大計数率 300 Mhz が可能になります。操作には明確に4つのモードがあり、各チャネルは ±10 V のレンジで調節可能な弁別器が搭載されています。時間領域とヒストグラム表示機能が付いたパルスカウンタによる測定結果は、で分析が可能なため便利です。これらのカウンタ値に基づいて、HDAWG 任意波形発生器 のブランチング条件を定義できるため、超高速早送りループで量子エラー修正が可能になります。

HDAWG-MF オプションにより、発振器の数が増え、HDAWG 多チャネル AWG の振幅変調機能が強化されます。マルチ周波数オプションでは、高速波形アップロードおよび搬送波周波数の柔軟微調整の向上によるメリットがあります。このメリットは、さまざまな重畳搬送波周波数が必要な用途で特に役立ちます。

HDAWG-ME メモリ拡張オプションは、 HDAWG 任意波形発生器 の利用可能な波形メモリをチャネルごとに 64 MSa からチャネルごとに 500 MSa まで拡張します。これにより、大量の波形処理が改善され、機器検査の高スループットおよび広帯域チャープまたはノイズ信号の生成に対応できるようになります。

HDAWG-PC リアルタイム 事前補償により、テスト対象デバイスの信号が HDAWG Arbitrary Waveform Generator で設計された信号と確実に一します。この機能は、逆フィルターリングの原理により、信号経路の不完全性の影響を最小限に抑えます。その中心となるのは、生成された波形がアナログ信号に変換される前にリアルタイムで適用される、広く構成可能なデジタルフィルターです。

FAQ よくある質問

技術資料

データシート

動画一覧

この製品に関するお問合せフォーム

フォームが表示されるまでしばらくお待ちください。

しばらくお待ちいただいてもフォームが表示されない場合、恐れ入りますが こちら までお問合せください。